# Jone eittel 126. com internat JZ4770

# JZ4770 Mobile Application Processor

# **Peripherals Programming Manual**

Copyright © 2005-2011 Ingenic Semiconductor Co. Ltd. All rights reserved.

# Disclaimer

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the usage, or intellectual property right infringement except as provided for by Ingenic Terms and Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this document without notice. Anyone relying on this documentation should contact Ingenic for the current interna documentation and errata.

Ingenic Semiconductor Co., Ltd.

Room 108, Building A, Information Center, Zhongguancun Software Park 8 Dongbeiwang West Road, Haidian District, Beijing, China, Tel: 86-10-82826661 Fax: 86-10-82825845 Http://www.ingenic.cn

# CONTENTS

| 1 Gen  | eral-Purpose I/O Ports                          | 1  |

|--------|-------------------------------------------------|----|

| 1.1 C  | Dverview                                        |    |

| 1.1.1  | GPIO Port A Summary                             | 2  |

| 1.1.2  | GPIO Port B Summary                             | 3  |

| 1.1.3  | GPIO Port C Summary                             | 4  |

| 1.1.4  | GPIO Port D Summary                             | 5  |

| 1.1.5  | GPIO Port E Summary                             | 6  |

| 1.1.6  | GPIO Port F Summary                             | 7  |

| 1.2 R  | Registers Description                           | 9  |

| 1.2.1  | PORT PIN Level Registers (PxPIN)                | 13 |

| 1.2.2  | PORT Interrupt Registers (PxINT)                |    |

| 1.2.3  | PORT Interrupt Set Registers (PxINTS)           |    |

| 1.2.4  | PORT Interrupt Clear Registers (PxINTC)         |    |

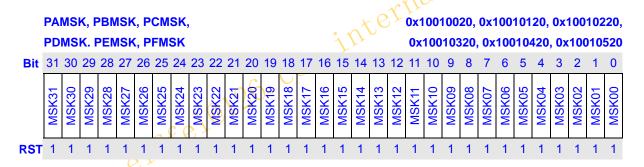

| 1.2.5  | PORT Mask Registers (PxMSK)                     |    |

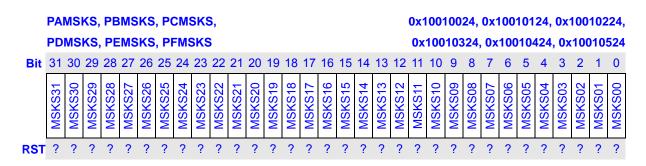

| 1.2.6  | PORT Mask Set Registers (PxMSKS)                |    |

| 1.2.7  | PORT Mask Clear Registers (PxMSKC)              |    |

| 1.2.8  | PORT PAT1/Direction Registers (PxPAT1)          | 17 |

| 1.2.9  | PORT PAT1/Direction Set Registers (PxPAT1S)     | 17 |

| 1.2.10 | ) PORT PAT1/Direction Clear Registers (PxPAT1C) |    |

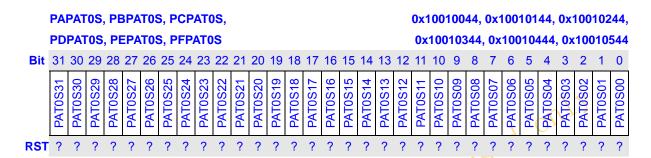

| 1.2.11 | PORT PAT0/Data Registers (PxPAT0)               |    |

| 1.2.12 | 2 PORT PAT0/Data Set Registers (PxPAT0S)        | 19 |

| 1.2.13 | B PORT PAT0/Data Clear Registers (PxPAT0C)      |    |

| 1.2.14 | PORT FLAG Registers (PxFLG)                     |    |

| 1.2.15 | 5 PORT FLAG Clear Registers (PxFLGC)            |    |

| 1.2.16 | PORT PULL Disable Registers (PxPE)              | 21 |

| 1.2.17 | PORT PULL Set Registers (PxPES)                 | 21 |

| 1.2.18 | B PORT PULL Clear Registers (PxPEC)             | 22 |

| 1.3 P  | Program Guide                                   |    |

| 1.3.1  | Port Function Guide                             |    |

| 2 I2C  | Controller                                      | 24 |

| 2.1 C  | Dverview                                        |    |

| 2.1.1  | Features                                        |    |

| 2.1.2  | Pin Description                                 |    |

| 2.2 R  | Registers                                       |    |

| 2.2.1  | Registers Memory Map                            |    |

| 2.2.2  | Registers and Fields Description                |    |

| 2.3 C  | Dperating Flow                                  |    |

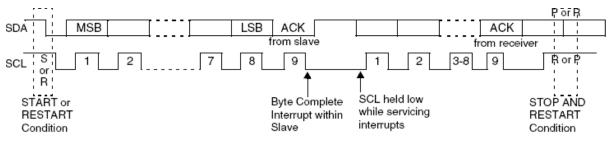

| 2.3.1  | I2C Behavior                                    |    |

| 2.3.2  | Master Mode Operation                           | 50 |

|        |                                                 | i  |

ii

| <ul> <li>2.3.4 Disabling I2C</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1       Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54 |

| <ul> <li>3.2 Pin Description</li> <li>3.3 Register Description</li> <li>3.3.1 SSI Data Register (SSIDR)</li> <li>3.3.2 SSI Control Register0 (SSICR0)</li> <li>3.3.3 SSI Control Register1 (SSICR1)</li> <li>3.3.4 SSI Status Register1 (SSISR)</li> <li>3.3.5 SSI Interval Time Control Register (SSIITR)</li> <li>3.3.6 SSI Interval Character-per-frame Control Register (SSIICR)</li> <li>3.3.7 SSI Clock Generator Register (SSIGR)</li> <li>3.4 Functional Description</li> </ul> | 56 |

| <ul> <li>3.2 Pin Description</li> <li>3.3 Register Description</li> <li>3.3.1 SSI Data Register (SSIDR)</li> <li>3.3.2 SSI Control Register0 (SSICR0)</li> <li>3.3.3 SSI Control Register1 (SSICR1)</li> <li>3.3.4 SSI Status Register1 (SSISR)</li> <li>3.3.5 SSI Interval Time Control Register (SSIITR)</li> <li>3.3.6 SSI Interval Character-per-frame Control Register (SSIICR)</li> <li>3.3.7 SSI Clock Generator Register (SSIGR)</li> <li>3.4 Functional Description</li> </ul> | 56 |

| <ul> <li>3.3 Register Description</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| <ul> <li>3.3.2 SSI Control Register0 (SSICR0)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| <ul> <li>3.3.3 SSI Control Register1 (SSICR1)</li> <li>3.3.4 SSI Status Register1 (SSISR)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                     | 58 |

| <ul> <li>3.3.4 SSI Status Register1 (SSISR)</li> <li>3.3.5 SSI Interval Time Control Register (SSIITR)</li> <li>3.3.6 SSI Interval Character-per-frame Control Register (SSIICR)</li> <li>3.3.7 SSI Clock Generator Register (SSIGR)</li> <li>3.4 Functional Description</li> </ul>                                                                                                                                                                                                     | 59 |

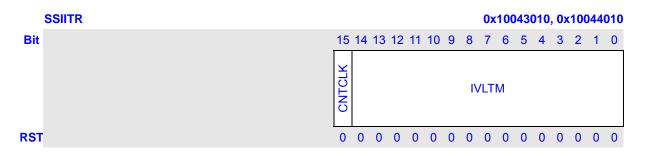

| <ul> <li>3.3.5 SSI Interval Time Control Register (SSIITR)</li> <li>3.3.6 SSI Interval Character-per-frame Control Register (SSIICR)</li> <li>3.3.7 SSI Clock Generator Register (SSIGR)</li> <li>3.4 Functional Description</li> </ul>                                                                                                                                                                                                                                                 | 61 |

| <ul> <li>3.3.6 SSI Interval Character-per-frame Control Register (SSIICR)</li> <li>3.3.7 SSI Clock Generator Register (SSIGR)</li> <li>3.4 Functional Description</li></ul>                                                                                                                                                                                                                                                                                                             | 64 |

| 3.3.7 SSI Clock Generator Register (SSIGR)                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66 |

| 3.4 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67 |

| 3.5 Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

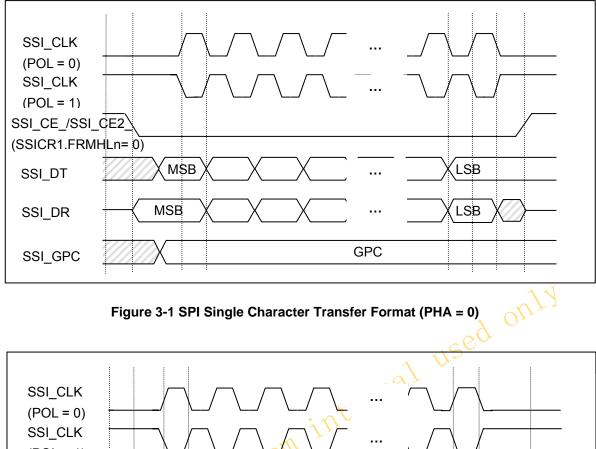

| 3.5.1 Motorola's SPI Format Details                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69 |

| 3.5.2 TI's SSP Format Details                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

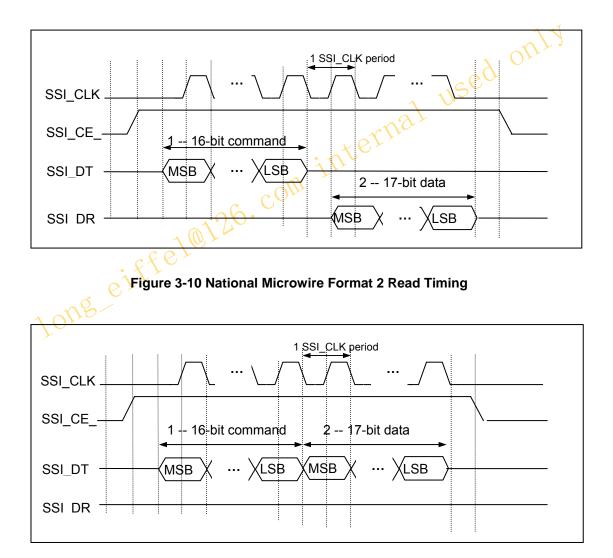

| 3.5.3 National Microwire Format Details                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| 3.6 Interrupt Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76 |

| <ul> <li>3.6 Interrupt Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77 |

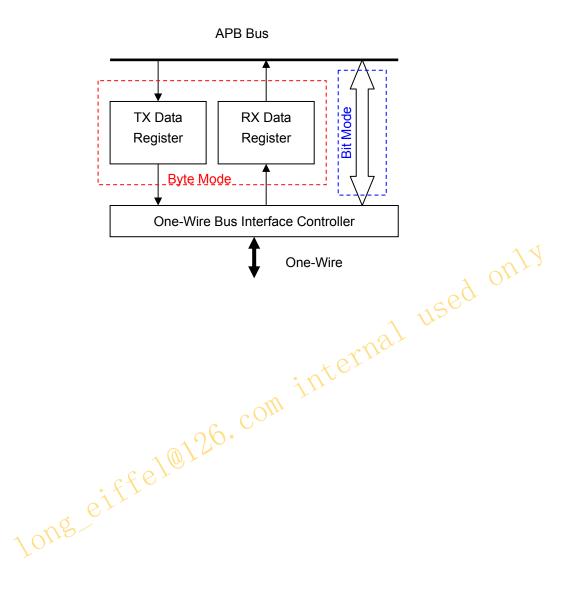

| 4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77 |

| 4.2 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 78 |

| 4.3 Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79 |

| 4.4 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4.4.1 One-Wire Configure Register (OWCFG)                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 |

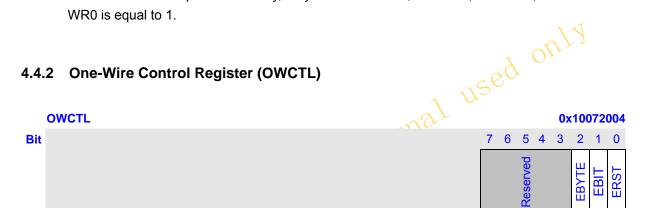

| 4.4.2 One-Wire Control Register (OWCTL)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 81 |

| 4.4.3 One-Wire Status Register (OWSTS)                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 81 |

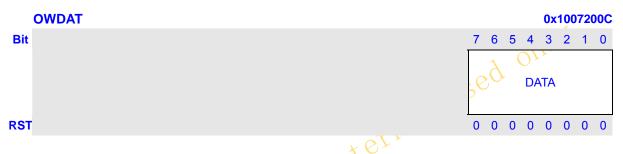

| 4.4.4 One-Wire Data Register (OWDAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82 |

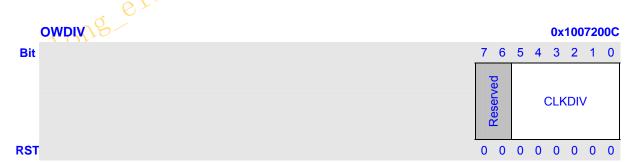

| 4.4.5 One-Wire Clock Divide Register (OWDIV)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82 |

| 4.5 One-Wire Bus Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83 |

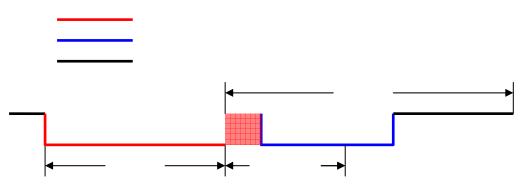

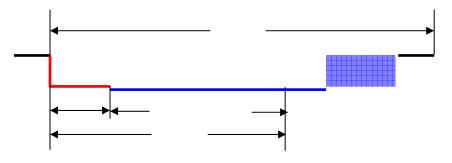

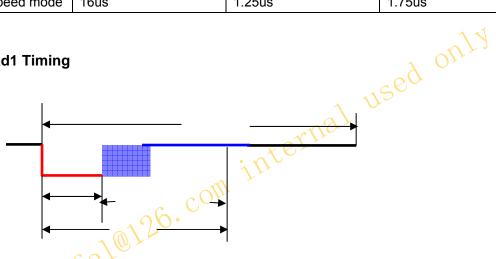

| 4.5.1 Reset Timing and ACK Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83 |

| 4.5.2 Write 0 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83 |

| 4.5.3 Write 1 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83 |

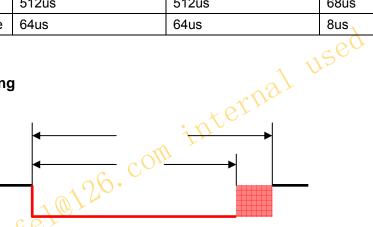

| 4.5.4 Read0 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84 |

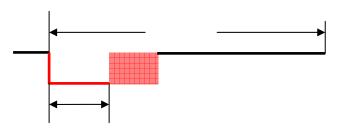

| 4.5.5 Read1 Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84 |

| 4.6 One-Wire Operation Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85 |

| 5 USB Host Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 5.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

| 5.2 Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 5.3 Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86 |

| 5 | .4    | Introduction                                     | 89  |

|---|-------|--------------------------------------------------|-----|

| 6 | OT    | ΓG Controller                                    |     |

| 6 | .1    | Overview                                         |     |

| 6 | .2    | Pin Description                                  | 91  |

| 6 | .3    | Register Description                             |     |

| 6 | .4    | Common registers                                 | 97  |

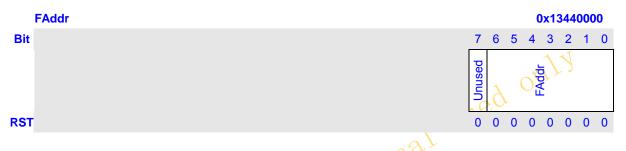

|   | 6.4.  | .1 FAddr                                         |     |

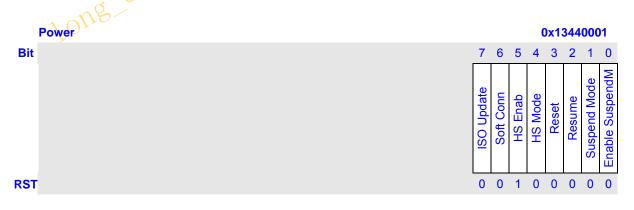

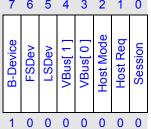

|   | 6.4.2 | .2 Power                                         | 97  |

|   | 6.4.3 | .3 IntrTx                                        |     |

|   | 6.4.4 | .4 IntrRx                                        |     |

|   | 6.4.  | .5 IntrTxE                                       | 100 |

|   | 6.4.6 | .6 IntrRxE                                       | 101 |

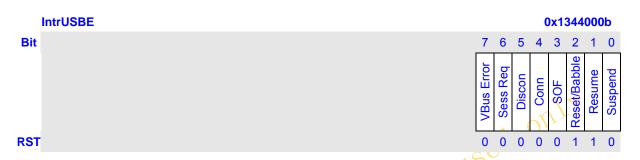

|   | 6.4.7 | .7 IntrUSB                                       | 102 |

|   | 6.4.8 |                                                  |     |

|   | 6.4.9 |                                                  |     |

|   | 6.4.  |                                                  | 104 |

|   | 6.4.1 |                                                  |     |

|   | 6.4.  |                                                  | 106 |

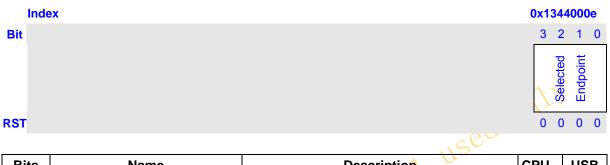

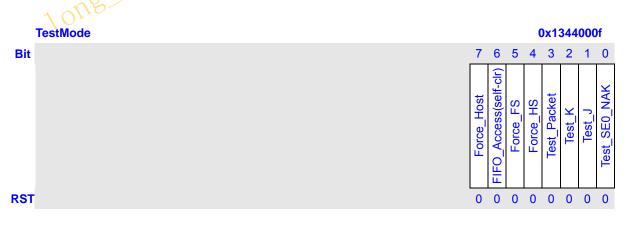

| 6 | .5    | Indexed Register                                 | 108 |

|   | 6.5.1 |                                                  |     |

|   | 6.5.2 | .2 Count0                                        | 111 |

|   | 6.5.3 |                                                  |     |

|   | 6.5.4 | .4 NakLimit0 (Host Mode Only)                    | 112 |

|   | 6.5.5 |                                                  |     |

|   | 6.5.6 | .6 TxCSR                                         | 114 |

|   | 6.5.7 | .7 RxMaxP                                        | 118 |

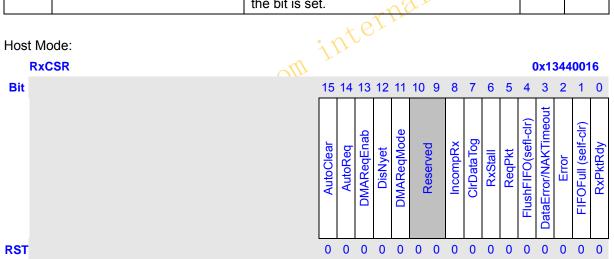

|   | 6.5.8 | .8 <b>R</b> xCSR                                 | 120 |

|   | 6.5.9 | 9 RxCount                                        | 124 |

|   | 6.5.  | .10 TxType (Host Mode Only)                      | 125 |

|   | 6.5.  | .11 TxInterval (Host Mode Only)                  | 125 |

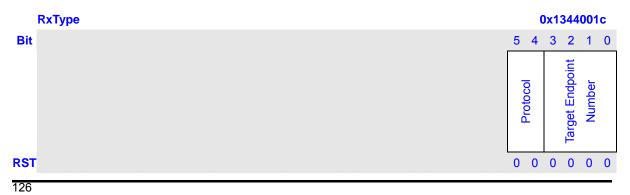

|   | 6.5.  | .12 RxType (Host Mode Only)                      | 126 |

|   | 6.5.  | .13 RxInterval                                   | 127 |

|   | 6.5.  | .14 FifoSize                                     | 128 |

|   | 6.5.  | .15 FIFOx                                        | 128 |

| 6 | .6    | Additional Multipoint Control / Status Registers | 129 |

|   | 6.6.  | .1 TxFuncAddr / RxFuncAddr                       | 129 |

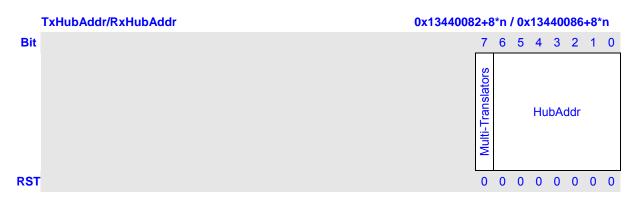

|   | 6.6.2 | .2 TxHubAddr/RxHubAddr                           | 129 |

|   | 6.6.3 | .3 TxHubPort / RxHubPort                         | 130 |

| 6 | .7    | Additional Control/Status Registers              | 131 |

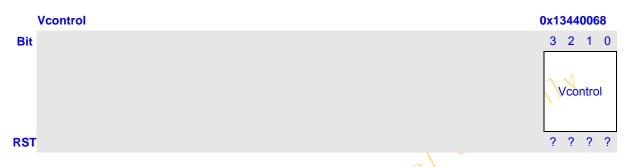

|   | 6.7.′ | .1 VControl                                      | 131 |

|   | 6.7.2 | .2 VStatus                                       | 131 |

|   | 6.7.3 | .3 Hwvers                                        | 132 |

| _ |       |                                                  | iii |

iv

| 6.8 Additional Configuration Registers                         |     |

|----------------------------------------------------------------|-----|

| 6.8.1 EPInfo                                                   |     |

| 6.8.2 RAMInfo                                                  |     |

| 6.8.3 LinkInfo                                                 | 134 |

| 6.8.4 VPLen                                                    | 134 |

| 6.8.5 HS_EOF1                                                  |     |

| 6.8.6 FS_EOF1                                                  | 135 |

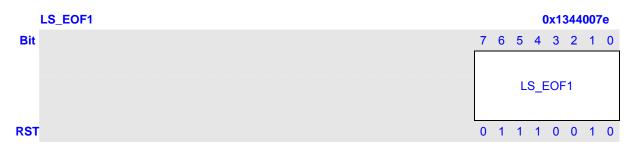

| 6.8.7 LS_EOF1                                                  | 136 |

| 6.8.8 SoftRst                                                  |     |

| 6.9 Extended Registers                                         | 138 |

| 6.9.1 RqPktCnt                                                 | 138 |

| 6.9.2 RmtWkIntr                                                | 138 |

| 6.9.3 RmtWkIntrE                                               | 139 |

| 6.9.4 RxDPktBufDis                                             |     |

| 6.9.5 TxDPktBufDis                                             |     |

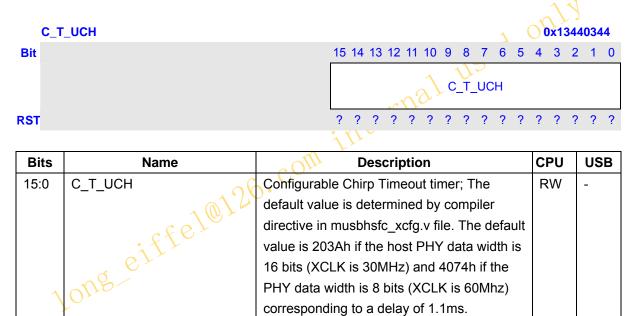

| 6.9.6 C_T_UCH                                                  |     |

| 6.9.7 C_T_HHSRTN                                               |     |

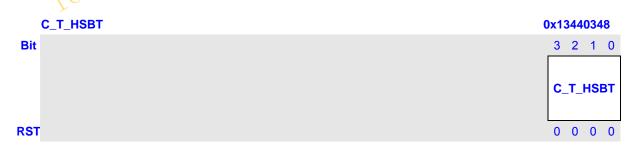

| 6.9.8 C_T_HSBT                                                 |     |

| 6.10 DMA Registers                                             | 144 |

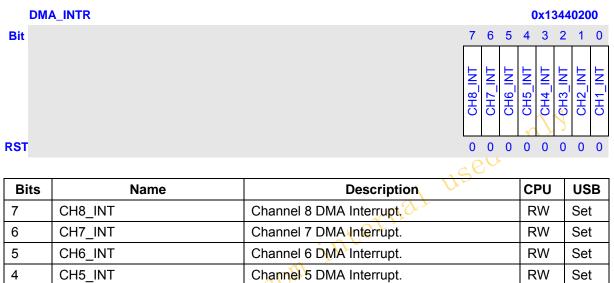

| 6.10.1 DMA_INTR                                                | 144 |

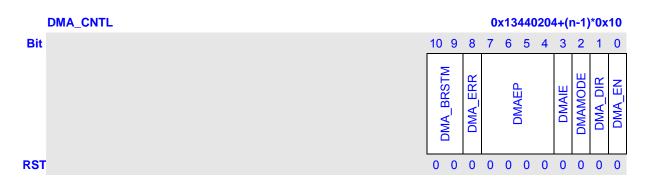

| 6.10.2 DMA_CNTL                                                | 144 |

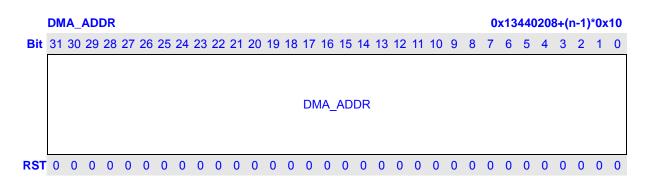

| 6.10.3 DMA_ADDR                                                | 145 |

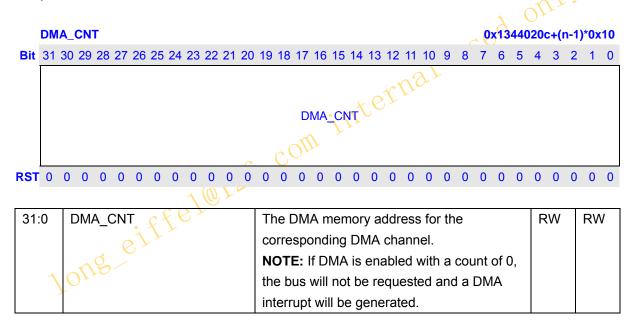

| 6.10.4 DMA_COUNT                                               |     |

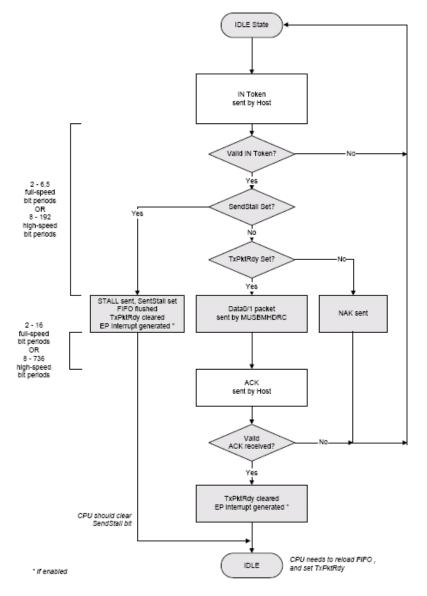

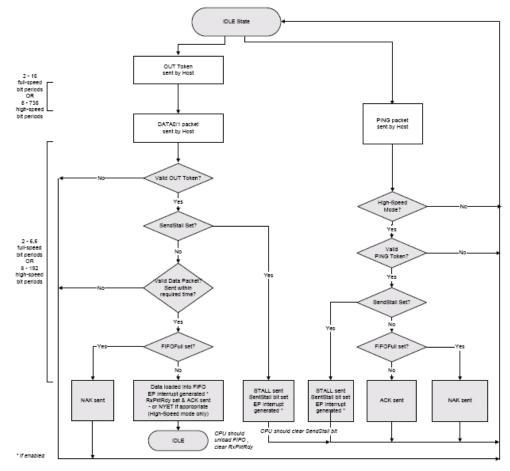

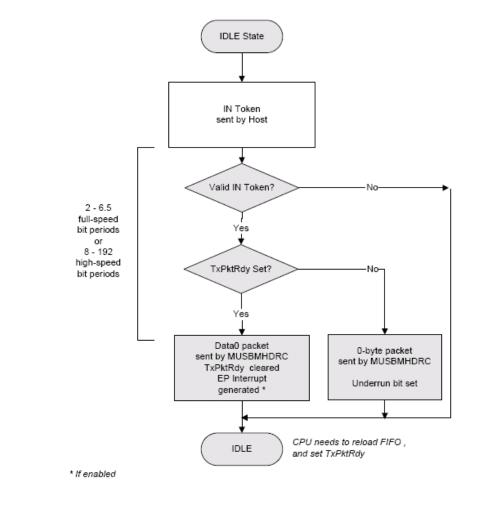

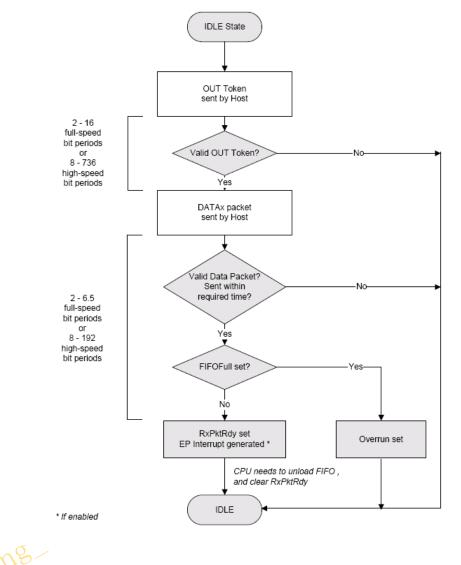

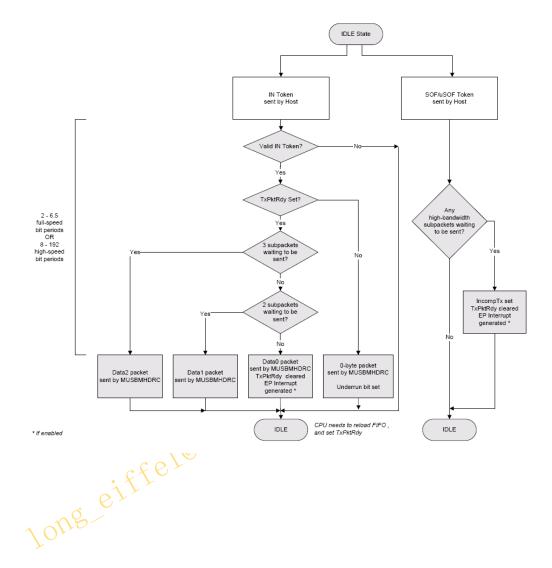

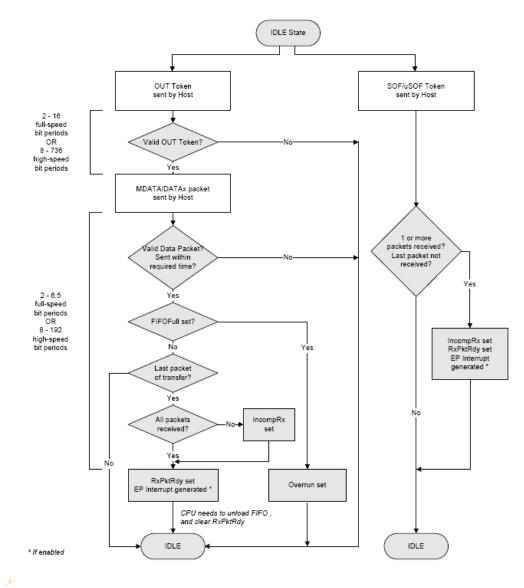

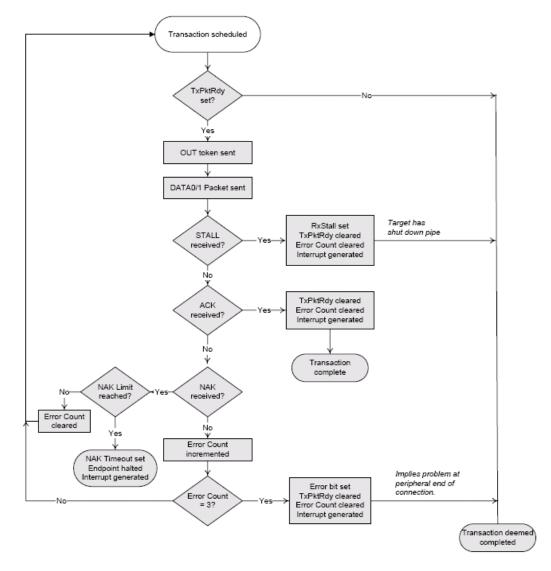

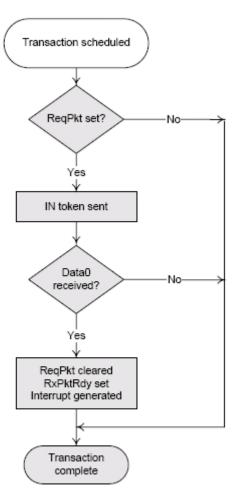

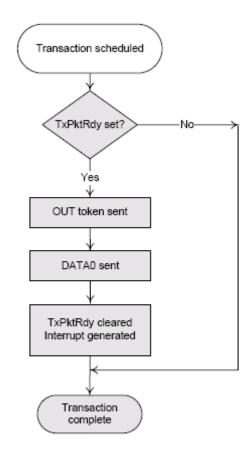

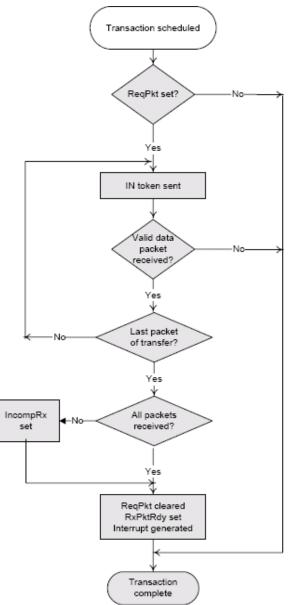

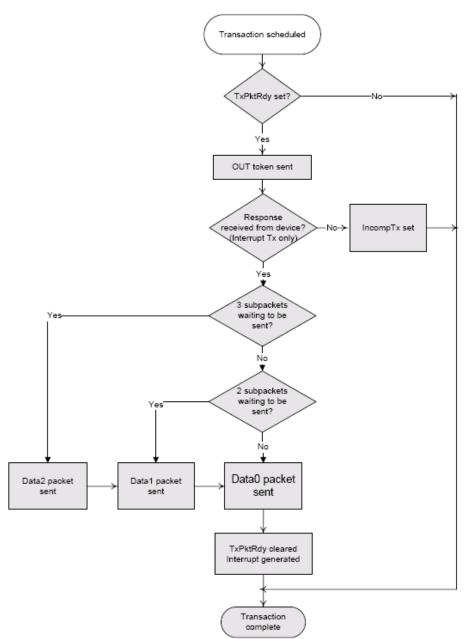

| 6.11 Transaction flows as a peripheral                         |     |

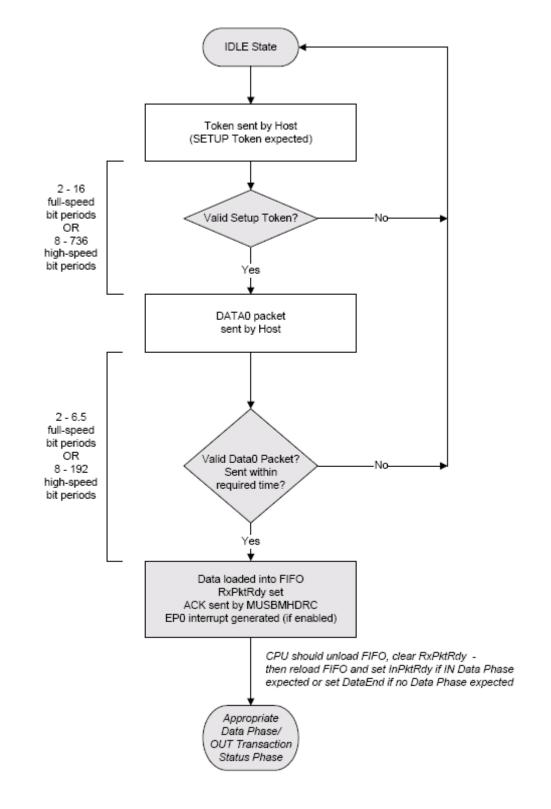

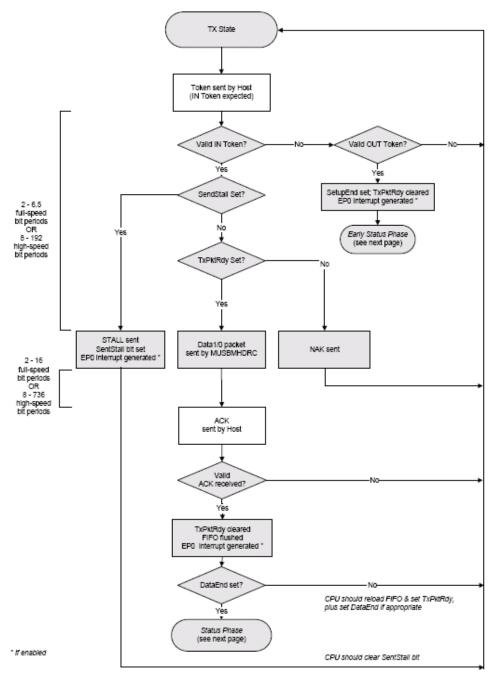

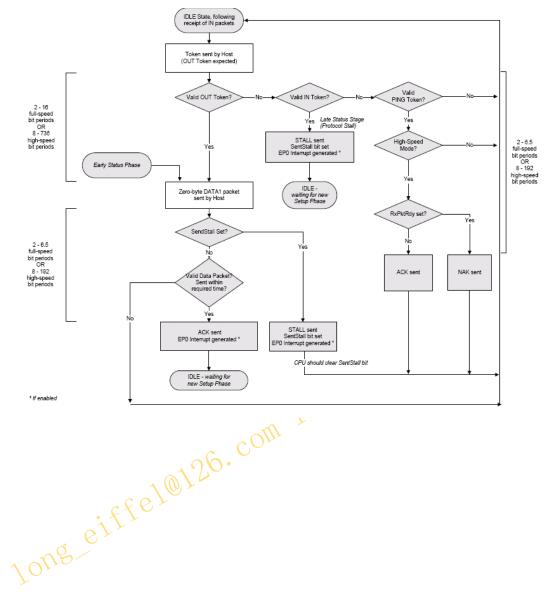

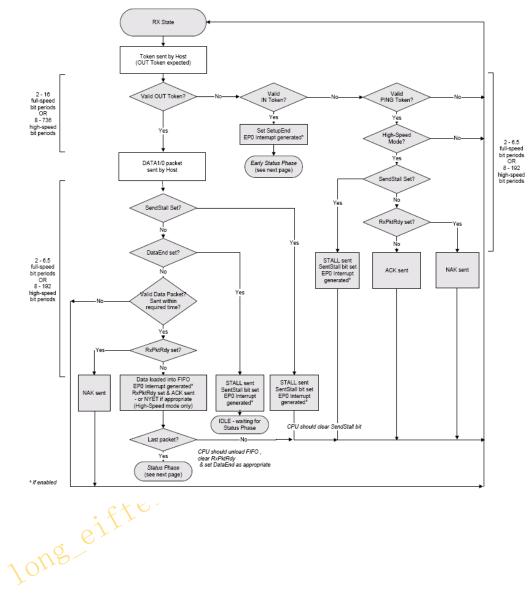

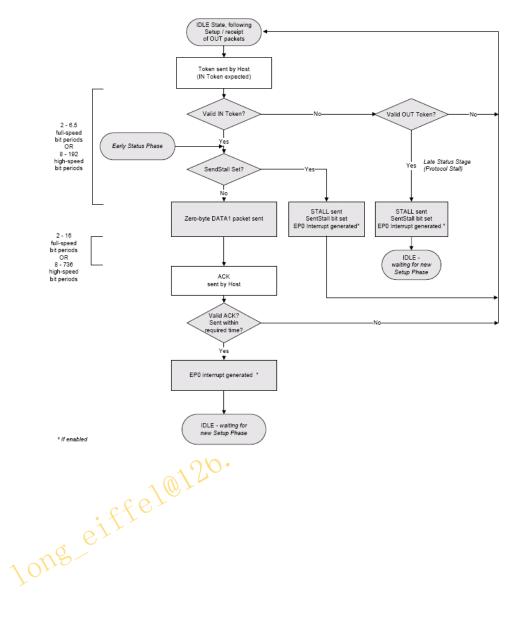

| 6.11.1 Control transactions                                    | 147 |

| 6.11.2 Bulk/Low-bandwidth interrupt transactions               |     |

| 6.11.3 Full-speed/Low-bandwidth isochronous transactions       |     |

| 6.11.4 High-bandwidth transactions (Isochronous and interrupt) |     |

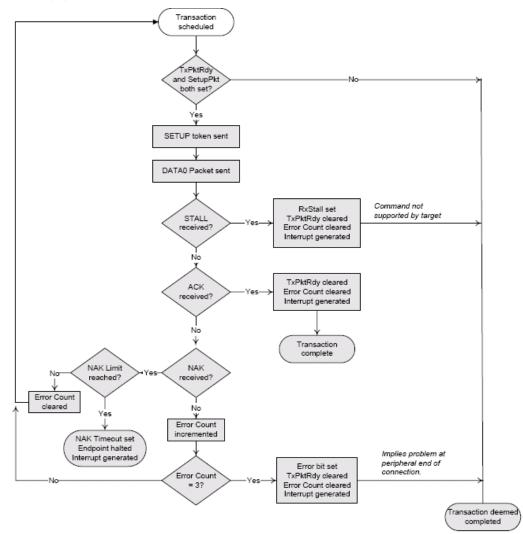

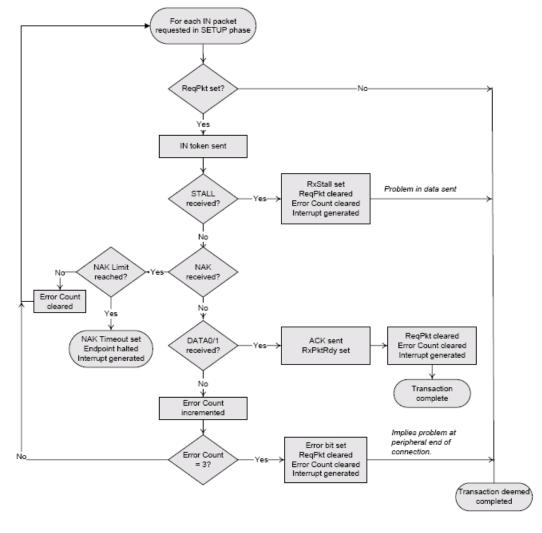

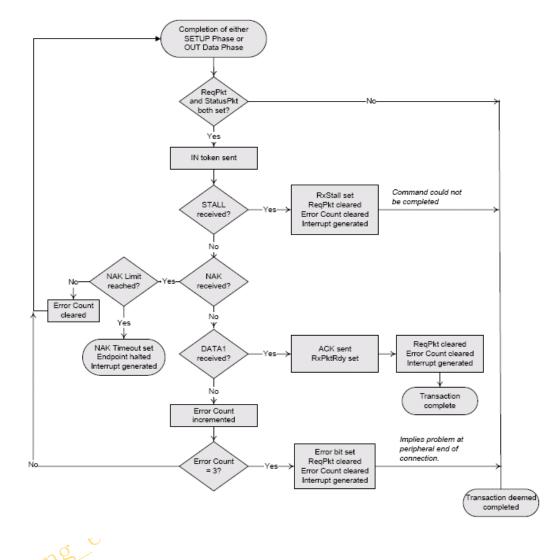

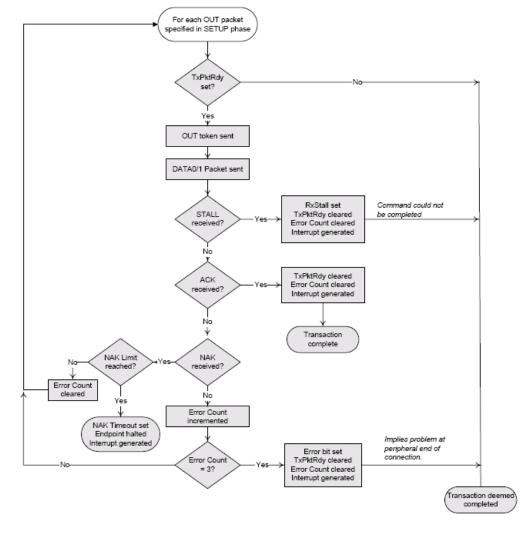

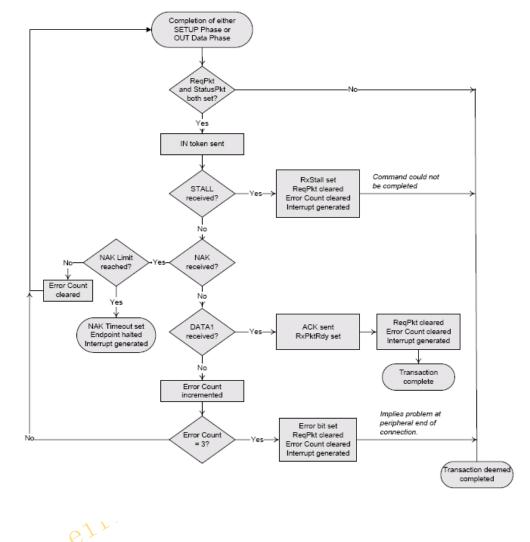

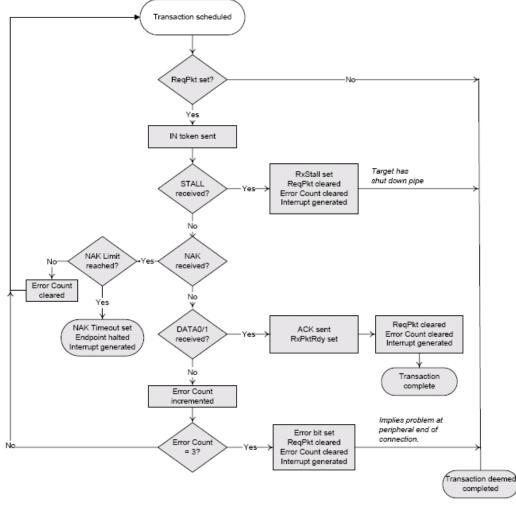

| 6.12 Transaction flows as a host                               | 158 |

| 6.12.1 Control transactions                                    |     |

| 6.12.2 Bulk/Low-bandwidth interrupt transactions               |     |

| 6.12.3 Full-speed/Low-bandwidth isochronous transactions       |     |

| 6.12.4 High-bandwidth transactions (isochronous and interrupt) |     |

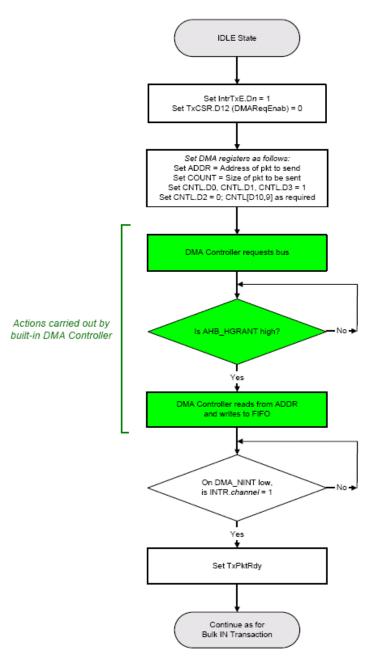

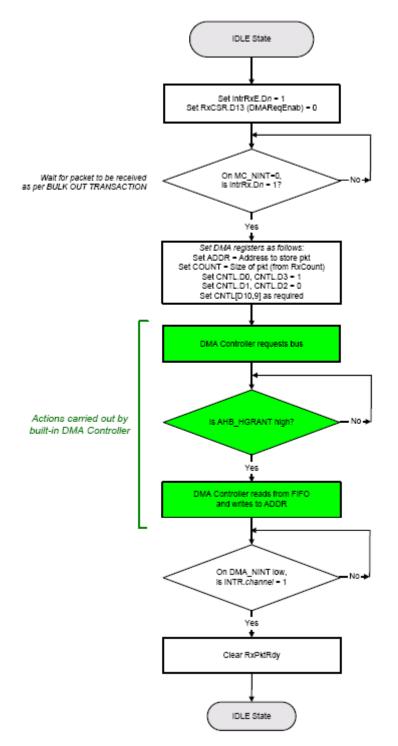

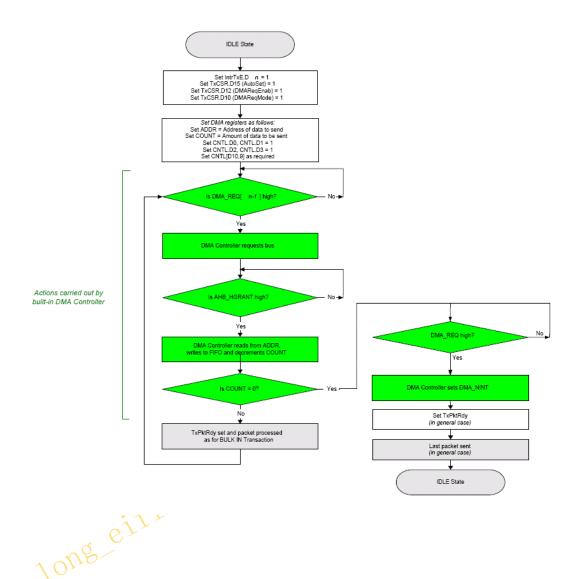

| 6.13 DMA operations                                            |     |

| 6.13.1 Single packet tx                                        |     |

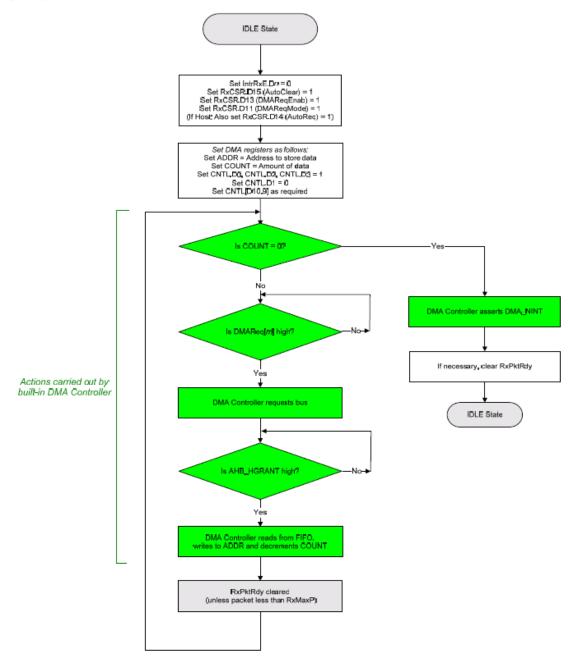

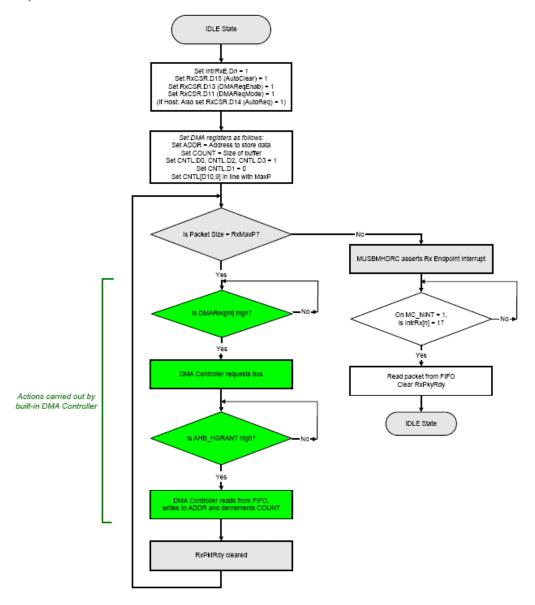

| 6.13.2 Single packet rx                                        | 170 |

| 6.13.3 Multiple packet tx                                      |     |

| 6.13.4 Multiple packet rx                                      |     |

| 7 MMC/SD CE-ATA Controller                                     | 174 |

| 7.1 Overview                                                   |     |

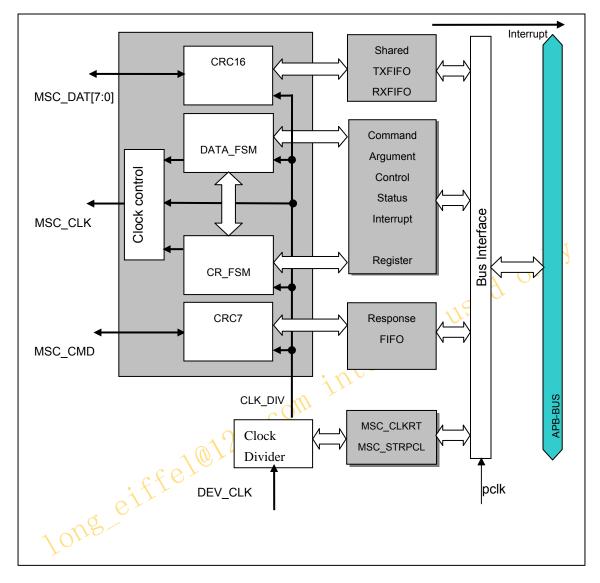

| 7.2 Block Diagram                                              |     |

| 7.3 MMC/SD Controller Signal I/O Description                   |     |

۷

| 7.4 R  | egister Description                                                  | 177 |

|--------|----------------------------------------------------------------------|-----|

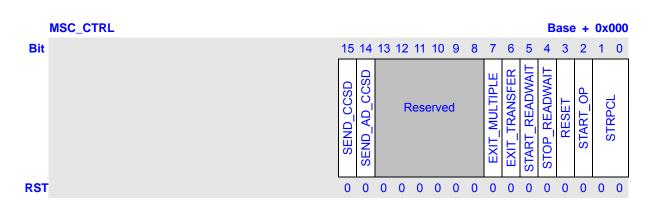

| 7.4.1  | MMC/SD Control Register (MSC_CTRL)                                   | 177 |

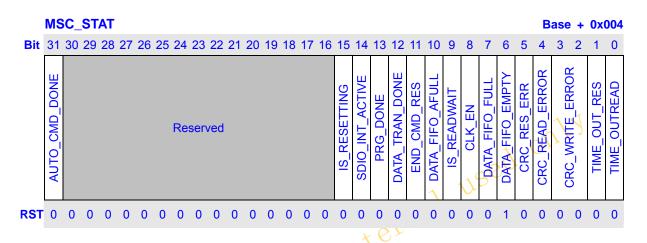

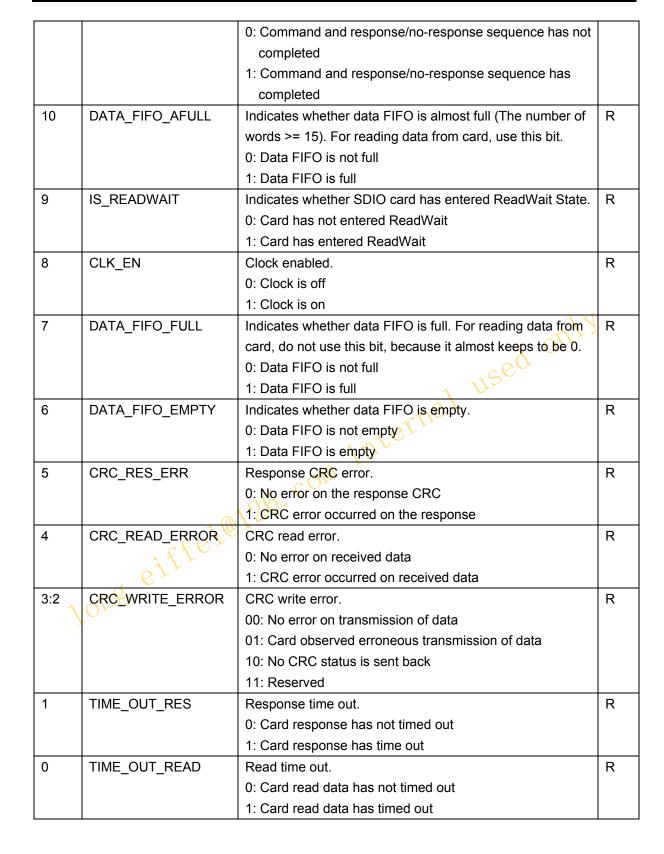

| 7.4.2  | MSC Status Register (MSC_STAT)                                       | 179 |

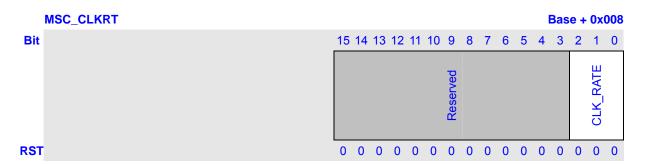

| 7.4.3  | MSC Clock Rate Register (MSC_CLKRT)                                  | 181 |

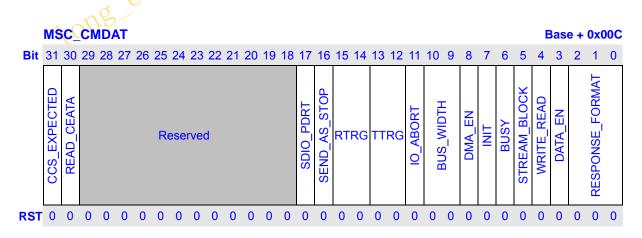

| 7.4.4  | MMC/SD Command and Data Control Register (MSC_CMDAT)                 | 181 |

| 7.4.5  | MMC/SD Response Time Out Register (MSC_RESTO)                        | 184 |

| 7.4.6  | MMC/SD Read Time Out Register (MSC_RDTO)                             | 184 |

| 7.4.7  | MMC/SD Block Length Register (MSC_BLKLEN)                            | 184 |

| 7.4.8  | MSC/SD Number of Block Register (MSC_NOB)                            | 185 |

| 7.4.9  | MMC/SD Number of Successfully-transferred Blocks Register (MSC_SNOB) | 185 |

| 7.4.10 | MMC/SD Interrupt Mask Register (MSC_IMASK)                           | 186 |

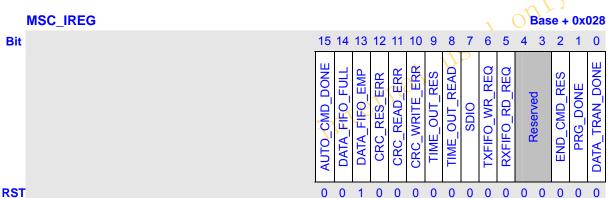

| 7.4.11 | MMC/SD Interrupt Register (MSC_IREG)                                 | 187 |

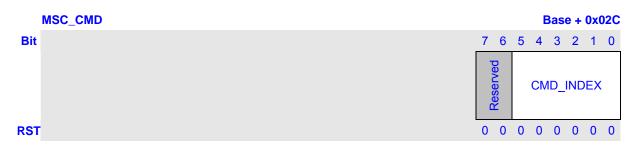

| 7.4.12 | MMC/SD Command Index Register (MSC_CMD)                              | 189 |

| 7.4.13 | MMC/SD Command Argument Register (MSC_ARG)                           | 189 |

| 7.4.14 | MMC/SD Response FIFO Register (MSC_RES)                              | 189 |

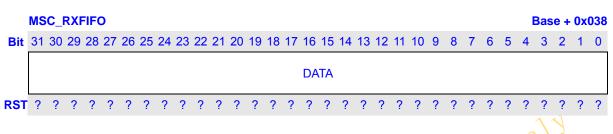

| 7.4.15 | MMC/SD Receive Data FIFO Register (MSC_RXFIFO)                       | 190 |

| 7.4.16 | MMC/SD Transmit Data FIFO Register (MSC_TXFIFO)                      | 190 |

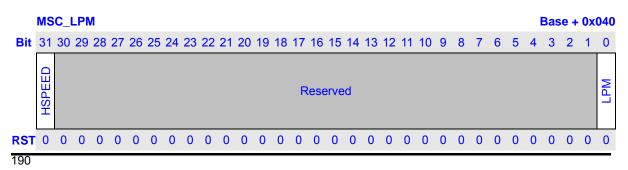

| 7.4.17 |                                                                      | 190 |

| 7.5 N  | MC/SD Functional Description                                         | 192 |

| 7.5.1  | MSC Reset                                                            | 192 |

| 7.5.2  | MSC Card Reset                                                       | 192 |

| 7.5.3  | Voltage ValidationCOT                                                | 192 |

| 7.5.4  | Card Registry                                                        | 193 |

| 7.5.5  | Card Access                                                          | 194 |

| 7.5.6  | Protection Management                                                | 195 |

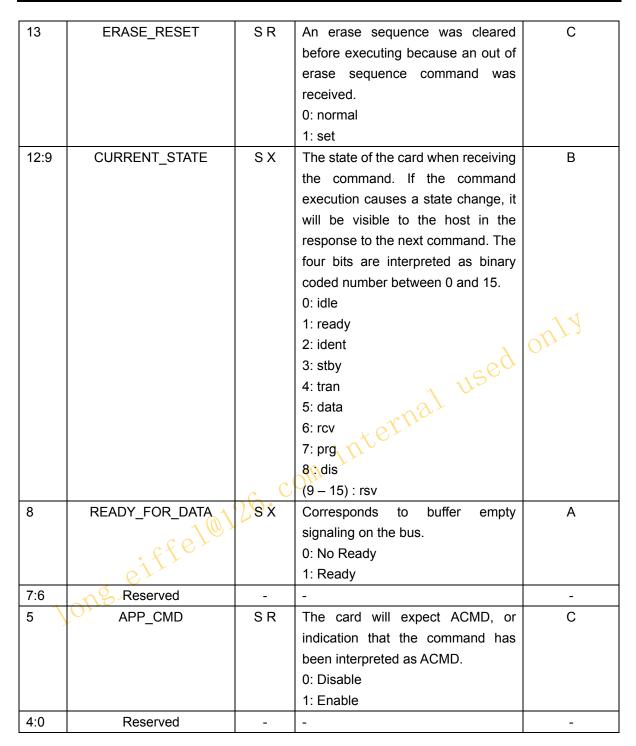

| 7.5.7  | Card Status                                                          | 199 |

| 7.5.8  | SD Status                                                            | 202 |

| 7.5.9  | ŚĘIJŎ                                                                | 203 |

| 7.5.10 | Clock Control                                                        | 205 |

| 7.5.11 | Application Specified Command Handling                               | 205 |

| 7.6 N  | MC/SD Controller Operation                                           | 207 |

| 7.6.1  | Data FIFOs                                                           | 207 |

| 7.6.2  | DMA and Program I/O                                                  | 208 |

| 7.6.3  | Start and Stop clock                                                 | 209 |

| 7.6.4  | Software Reset                                                       | 209 |

| 7.6.5  | Voltage Validation and Card Registry                                 | 210 |

| 7.6.6  | Single Data Block Write                                              | 211 |

| 7.6.7  | Single Block Read                                                    | 212 |

| 7.6.8  | Multiple Block Write                                                 | 212 |

| 7.6.9  | Multiple Block Read                                                  | 213 |

| 7.6.10 | Stream Write (MMC)                                                   | 214 |

| 7.6.11 | Stream Read (MMC)                                                    | 215 |

| 7.6.12 | Erase, Select/Deselect and Stop                                      | 216 |

|        |                                                                      |     |

|   | 7.6.13  | SDIO Suspend/Resume                                  | 216 |

|---|---------|------------------------------------------------------|-----|

|   | 7.6.14  | SDIO ReadWait                                        | 216 |

|   | 7.6.15  | Operation and Interrupt                              | 217 |

| 8 | UART    | Interface                                            | 219 |

| 8 | .1 Ove  | rview                                                | 219 |

|   | 8.1.1   | Features                                             | 219 |

|   | 8.1.2   | Pin Description                                      | 219 |

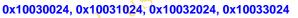

| 8 | .2 Reg  | ister Descriptions                                   | 220 |

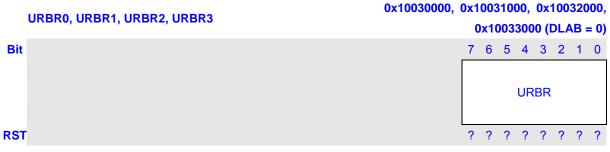

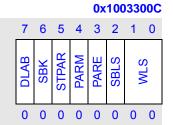

|   | 8.2.1   | UART Receive Buffer Register (URBR)                  | 221 |

|   | 8.2.2   | UART Transmit Hold Register (UTHR)                   | 222 |

|   | 8.2.3   | UART Divisor Latch Low/High Register (UDLLR / UDLHR) | 222 |

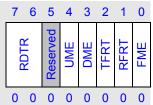

|   | 8.2.4   | UART Interrupt Enable Register (UIER)                | 223 |

|   | 8.2.5   | UART Interrupt Identification Register (UIIR)        | 224 |

|   | 8.2.6   | UART FIFO Control Register (UFCR)                    |     |

|   | 8.2.7   | UART Line Control Register (ULCR)                    | 226 |

|   | 8.2.8   | UART Line Status Register (ULSR)                     | 227 |

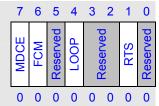

|   | 8.2.9   | UART Modem Control Register (UMCR)                   | 229 |

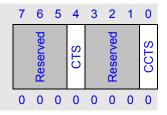

|   | 8.2.10  | UART Modem Status Register (UMSR)                    | 230 |

|   | 8.2.11  | UART Scratchpad Register                             | 231 |

|   | 8.2.12  | Infrared Selection Register (ISR)                    |     |

|   | 8.2.13  | UART M Register (UMR)                                | 232 |

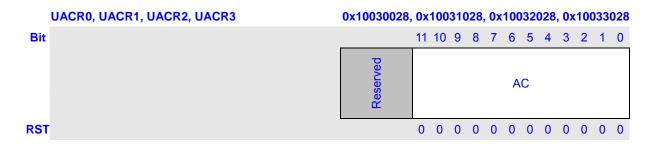

|   | 8.2.14  | UART Add Cycle Register (UACR)                       | 232 |

| 8 | .3 Ope  | ration                                               | 233 |

|   | 8.3.1   | UART Configuration                                   | 233 |

|   | 8.3.2   | Data Transmission                                    | 233 |

|   | 8.3.3   | Data Reception                                       | 233 |

|   | 8.3.4 🔨 | Receive Error Handling                               | 234 |

|   | 8.3.5   | Modem Transfer                                       | 234 |

|   | 8.3.6   | DMA Transfer                                         | 234 |

|   | 8.3.7   | Slow IrDA Asynchronous Interface                     | 235 |

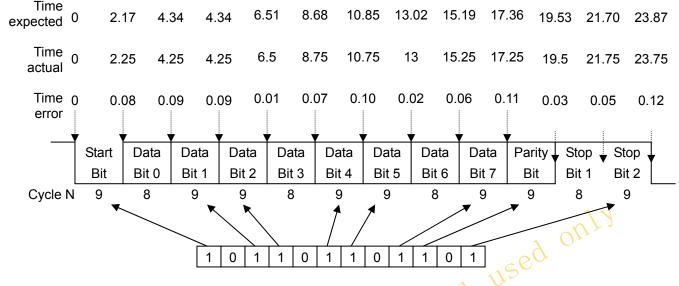

|   | 8.3.8   | For any frequency clock to use the UART              | 235 |

| 9 | Smart   | Card Controller                                      | 238 |

| 9 | .1 Ove  | rview                                                | 238 |

| 9 | .2 Pin  | Description                                          | 239 |

| 9 | .3 Reg  | ister Description                                    | 240 |

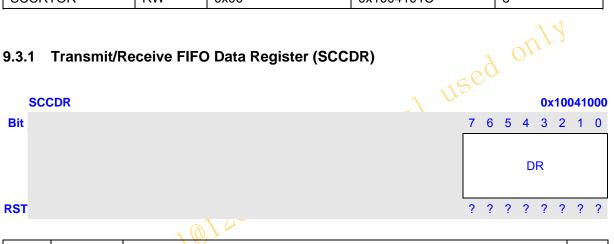

|   | 9.3.1   | Transmit/Receive FIFO Data Register (SCCDR)          | 240 |

|   | 9.3.2   | FIFO Data Count Register (SCCFDR)                    | 240 |

|   | 9.3.3   | Control Register (SCCCR)                             |     |

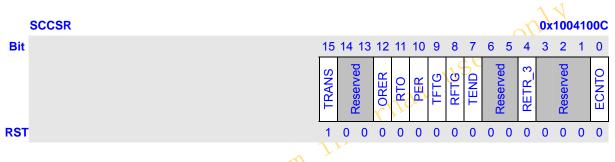

|   | 9.3.4   | Status Register (SCCSR)                              |     |

|   | 9.3.5   | Transmission Factor Register (SCCTFR)                |     |

|   | 9.3.6   | Extra Guard Timer Register (SCCEGTR)                 | 243 |

vi

| 9.3.7     | ETU Counter Value Register (SCCECR)                                    |     |

|-----------|------------------------------------------------------------------------|-----|

| 9.3.8     | Reception Timeout Register (SCCRTOR)                                   |     |

| 10 TS Sla | ave Interface (TSSI)                                                   |     |

| 10.1 Ove  | erview                                                                 |     |

| 10.2 Pin  | Description                                                            |     |

| 10.3 Reg  | gister Description                                                     |     |

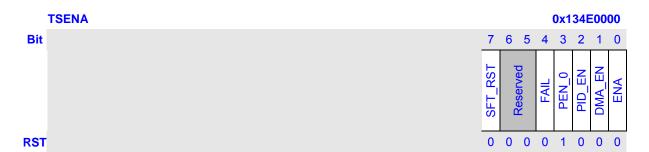

| 10.3.1    | TSSI Enable Register (TSENA)                                           |     |

| 10.3.2    | TSSI Configure Register (TSCFG)                                        |     |

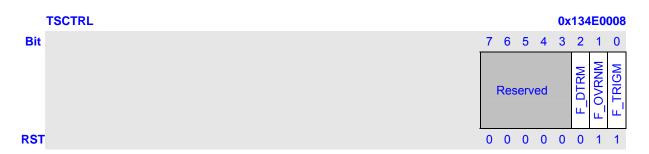

| 10.3.3    | TSSI Control Register (TSCTRL)                                         |     |

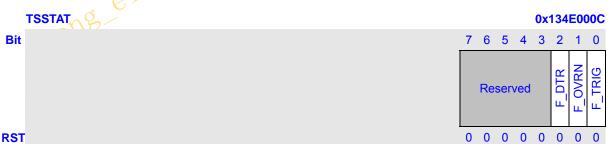

| 10.3.4    | TSSI State Register (TSSTAT)                                           |     |

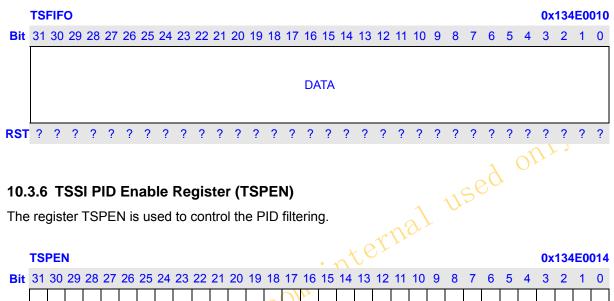

| 10.3.5    | TSSI FIFO Register (TSFIFO)                                            |     |

| 10.3.6    | TSSI PID Enable Register (TSPEN)                                       |     |

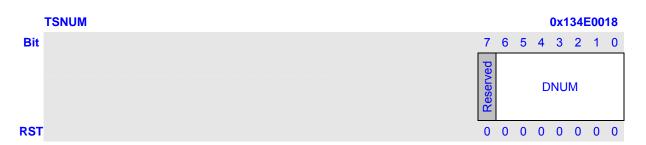

| 10.3.7    | TSSI Data Number Register (TSNUM)                                      |     |

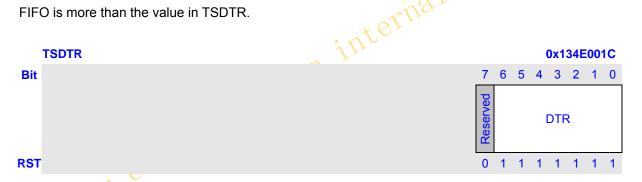

| 10.3.8    | TSSI Data Trigger Register (TSDTR)                                     |     |

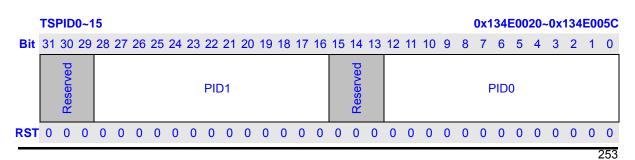

| 10.3.9    | TSSI PID Filter Registers (TSPID0~15)                                  |     |

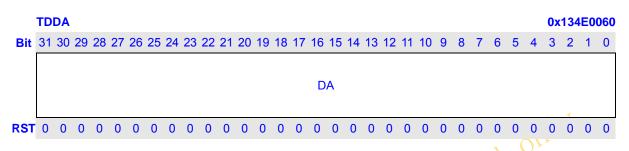

| 10.3.10   | TSSI DMA Descriptor Address (TSDDA)<br>TSSI DMA Target Address (TSDTA) |     |

| 10.3.11   | TSSI DMA Target Address (TSDTA)                                        |     |

| 10.3.12   | TSSI DMA Identifier (TSDID)                                            |     |

| 10.3.13   | TSSI DMA Command (TSDCMD)                                              |     |

| 10.3.14   | TSST DMA Status (TSDST)                                                |     |

| 10.3.15   | TSSI Transfer Control Register (TSTC)                                  |     |

|           | SI Timing                                                              |     |

| 10.5 TSS  | SI Guide                                                               |     |

| 10.5.1    | TSSI Operation without PID Filtering Function                          |     |

| 10.5.2    | TSSI Operation with PID Filtering Function                             |     |

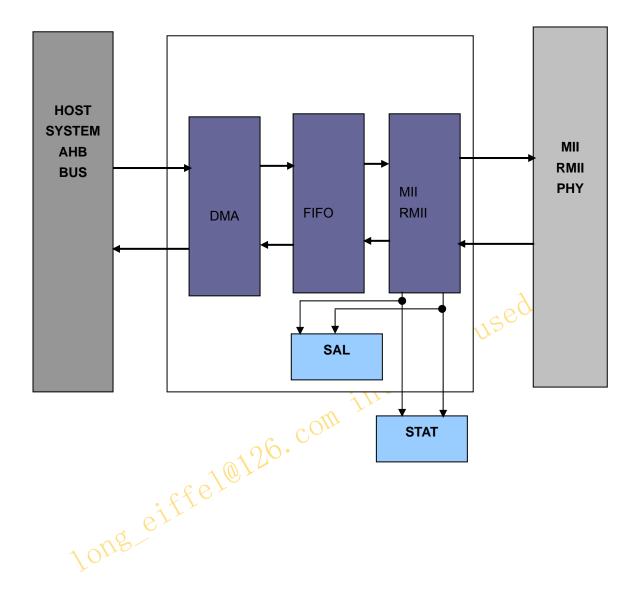

| 11 Etherr | net MAC Controller                                                     |     |

| 11.1 Ove  | svo-                                                                   |     |

| × 1       | AN support Ethernet Signals                                            |     |

|           | ck Diagram                                                             |     |

|           | A Module                                                               |     |

| 11.4.1    | Overview                                                               |     |

| 11.4.2    | Features                                                               |     |

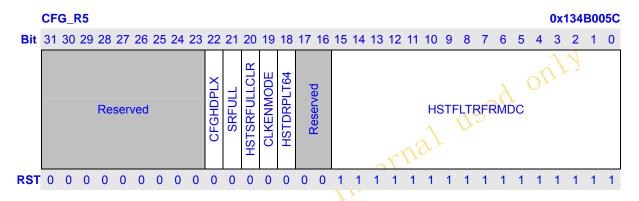

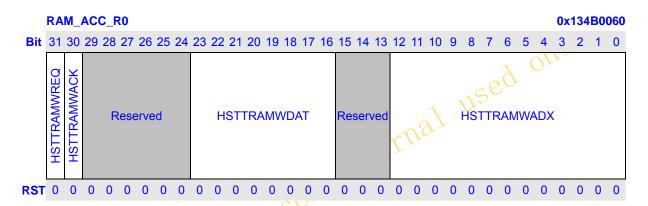

| 11.4.3    | Register Map                                                           |     |

| 11.4.4    | Register Description                                                   |     |

| 11.5 FIF  | O Module                                                               |     |

| 11.5.1    | Overview                                                               |     |

| 11.5.2    | Features                                                               |     |

| 11.5.3    | Register Map                                                           |     |

| 11.5.4    | Register Description                                                   |     |

|           | Module                                                                 |     |

| 11.6.1    | Overview                                                               |     |

|           |                                                                        | vii |

viii

| 11.6.2    | Register Map                    |     |

|-----------|---------------------------------|-----|

| 11.6.3    | Register Description            |     |

| 11.7 RM   | II Module                       |     |

| 11.7.1    | Overview                        |     |

| 11.7.2    | Feature                         |     |

| 11.8 SAL  | _ Module                        |     |

| 11.8.1    | Overview                        |     |

| 11.8.2    | Register Map                    |     |

| 11.8.3    | Register Description            |     |

| 11.9 STA  | NT Module                       |     |

| 11.9.1    | Overview                        |     |

| 11.9.2    | Register Map                    |     |

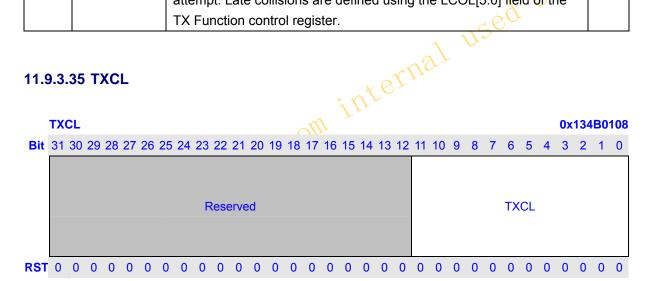

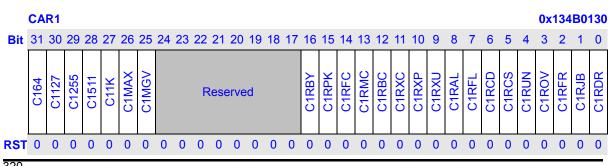

| 11.9.3    | Register Description            |     |

|           | E Clave Interface (EELICE)      | 205 |

| 12 EFU5   | E Slave Interface (EFUSE)       |     |

| 12.1 Ove  | erview                          |     |

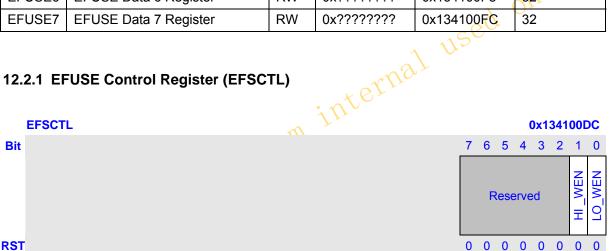

| 12.2 Reg  | jister Description              | 326 |

| 12.2.1    | EFUSE Control Register (EFSCTL) |     |

| 12.2.2    | EFUSE Data Register (EFUSEn)    |     |

| 12.3 Flow | N                               |     |

| 12.3.1    | Write EFUSE Flow                |     |

| 12.3.2    | Read EFUSE Flow                 |     |

| 100       | E Oldve Interface (EFOOL)       |     |

i

# TABLES

| Table 1-1 GPIO Port A summary                                | 2   |

|--------------------------------------------------------------|-----|

| Table 1-2 GPIO Port B summary                                | 3   |

| Table 1-3 GPIO Port C summary                                | 4   |

| Table 1-4 GPIO Port D summary                                | 5   |

| Table 1-5 GPIO Port E summary                                | 6   |

| Table 1-6 GPIO Port F summary                                | 7   |

| Table 1-7 GPIO Registers                                     | 9   |

| Table 2-1 I2C Pin Description                                | 24  |

| Table 2-2 Registers Memory Map-Address Base                  | 26  |

| Table 2-3 Registers Memory Map-Address Offset                | 26  |

| Table 3-1 Micro Printer Controller Pins Description          | 57  |

| Table 3-2 SSI Serial Port Registers                          | 58  |

| Table 3-3 SSI Interrupts                                     | 76  |

| Table 4-1 One-Wire Controller Pins Description               | 78  |

| Table 4-2 OWI Registers Description                          | 80  |

| Table 5-1 UHC Pins Description                               | 87  |

| Table 6-1 OTG Pins Description                               | 91  |

| Iable 6-2 UTU- Redisters Description                         | y 2 |

| Table 7-1 Command Token Format                               | 176 |

| Table 7-2 MMC/SD Data Token Format                           | 176 |

| Table 7-3 MMC/SD Controller Registers Description            | 177 |

| Table 7-4 Command Data Block Structure                       | 196 |

| Table 7-5 Card Status Description                            | 200 |

| Table 7-6 SD Status Structure                                | 203 |

| Table 7-7 How to stop multiple block write                   | 213 |

| Table 7-8 How to stop multiple block read                    | 214 |

| Table 7-9 The mapping between Commands and Steps             | 217 |

| Table 8-1 UART Pins Description                              | 219 |

| Table 8-2 UART Registers Description                         | 220 |

| Table 8-3 UART Interrupt Identification Register Description | 224 |

| Table 9-1 Smart Card Controller Pins Description             | 239 |

| Table 9-2 Smart Card Controller Registers Description        | 240 |

| Table 10-1 TSSI Pin Description                              | 246 |

| Table 10-2 TSSI Register Description                         | 247 |

| Table 11-1 Ethernet MII Signals                              | 261 |

| Table 11-2 Pin Map of MII and RMII Mode                      | 262 |

|                                                              |     |

Long\_eiffel@126.com internal used only

i

# FIGURES

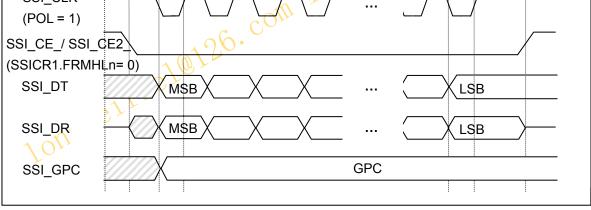

| Figure 3-1 SPI Single Character Transfer Format (PHA = 0)                | 70    |

|--------------------------------------------------------------------------|-------|

| Figure 3-2 SPI Single Character Transfer Format (PHA = 1)                | 70    |

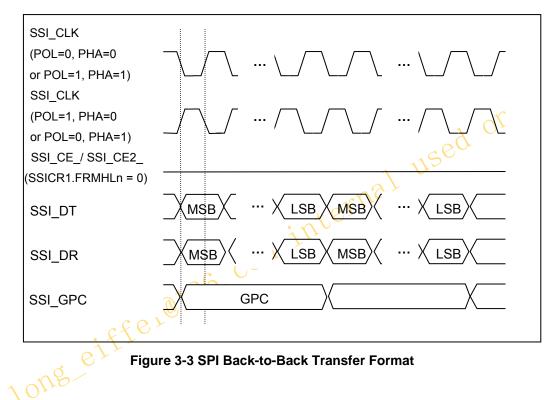

| Figure 3-3 SPI Back-to-Back Transfer Format                              | 71    |

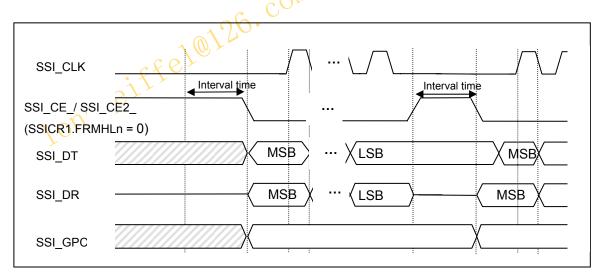

| Figure 3-4 SPI Frame Interval Mode Transfer Format (ITFRM = 0, LFST = 0) | 72    |

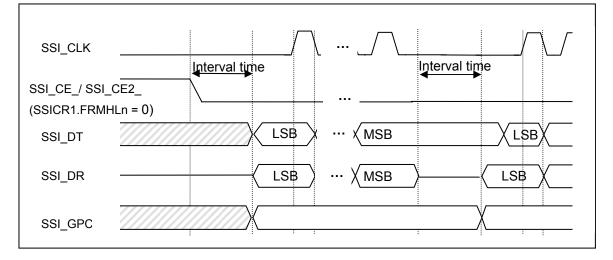

| Figure 3-5 SPI Frame Interval Mode Transfer Format (ITFRM = 1, LFST = 1) | 73    |

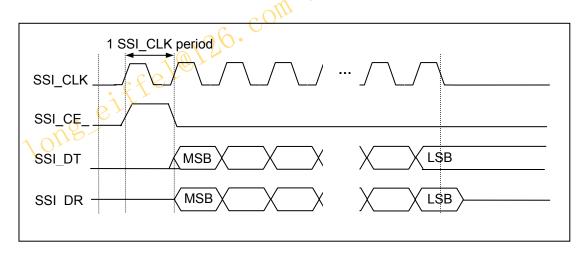

| Figure 3-6 TI's SSP Single Transfer Format                               | 73    |

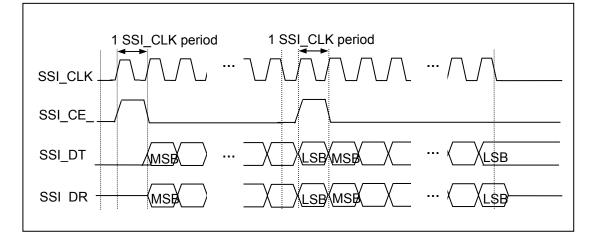

| Figure 3-7 TI's SSP Back-to-back Transfer Format                         | 74    |

| Figure 3-8 National Microwire Format 1 Single Transfer                   | 74    |

| Figure 3-9 National Microwire Format 1 Back-to-back Transfer             | 75    |

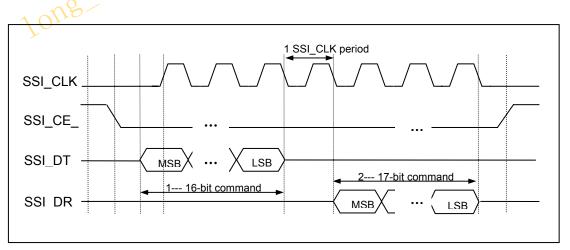

| Figure 3-10 National Microwire Format 2 Read Timing                      | 75    |

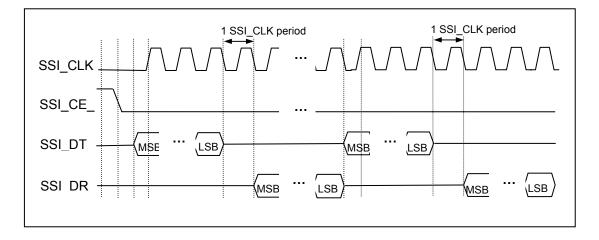

| Figure 3-11 National Microwire Format 2 Write Timing                     | 75    |

| Figure 7-1 MMC/SD CE-ATA Controller Block Diagram                        | . 175 |

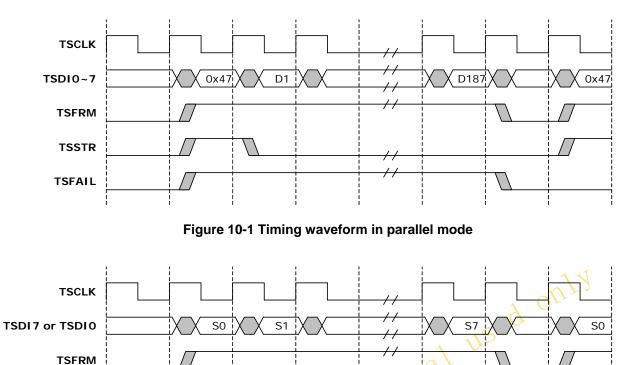

| Figure 10-1 Timing waveform in parallel mode                             | . 258 |

| Figure 10-2 Timing waveform in serial mode                               | . 258 |

| - Pot                                                                    |       |

| 21 45                                                                    |       |

| internal use                                                             |       |

| om internal use                                                          |       |

| 26. COM internal use                                                     |       |

| 126. com internal use                                                    |       |

| scol@126.com internal use                                                |       |

| iffel@126.com internal use                                               |       |

| eiffel@126.com internal use                                              |       |

| 1008_eiffel@126.com internal use                                         |       |

| 10ng_eiffel@126.com internal use                                         |       |

| Figure 10-1 Timing waveform in parallel mode                             |       |

Long\_eiffel@126.com internal used only

#### **General-Purpose I/O Ports** 1

#### **Overview** 1.1

General Purpose I/O Ports (GPIO) is used in generating and capturing application-specific input and output signals. Each port can be programmed as an output, an input or function port that serves certain peripheral. As input, pull up/down can be enabled/disabled for the port and the port also can be configured as level or edge tripped interrupt source.

#### Features:

- Each port can be configured as an input, an output or an alternate function port

- Each port can be configured as an interrupt source of low/high level or rising/falling edge triggering. • Every interrupt source can be masked independently

- " The pull-u usi internal usi internal usi internal usi Each port has an internal pull-up or pull-down resistor connected. The pull-up/down resistor can • be disabled

- GPIO output 6 interrupts, 1 for every group, to INTC

# 1.1.1 GPIO Port A Summary

| Bit | ΡΑ | Pull   |             | Shared Fund  | ction Port Selecte | ed by                   |      |

|-----|----|--------|-------------|--------------|--------------------|-------------------------|------|

| Ν   | Ν  | (U/D)  | 0           | 1            | 2                  | 3                       | Note |

| 0   | 00 | U      | sd0(io)     | -            | -                  | -                       |      |

| 1   | 01 | U      | sd1(io)     | -            | -                  | -                       |      |

| 2   | 02 | U      | sd2(io)     | -            | -                  | -                       |      |

| 3   | 03 | U      | sd3(io)     | -            | -                  | -                       |      |

| 4   | 04 | U      | sd4(io)     | -            | -                  | -                       |      |

| 5   | 05 | U      | sd5(io)     | -            | -                  | -                       |      |

| 6   | 06 | U      | sd6(io)     | -            | -                  | -                       |      |

| 7   | 07 | U      | sd7(io)     | -            | -                  | -                       | 1    |

| 8   | 08 | U      | sd8(io)     | -            | -                  | -                       | 7    |

| 9   | 09 | U      | sd9(io)     | -            | -                  | - 2 01                  |      |

| 10  | 10 | U      | sd10(io)    | -            | -                  | 1500                    |      |

| 11  | 11 | U      | sd11(io)    | -            | - 1                | $\overline{\Omega_{r}}$ |      |

| 12  | 12 | U      | sd12(io)    | -            | - rhat             | -                       |      |

| 13  | 13 | U      | sd13(io)    | -            | J.Cr               | -                       |      |

| 14  | 14 | U      | sd14(io)    | -            | -                  | -                       |      |

| 15  | 15 | U      | sd15(io)    | -            | -                  | -                       |      |

| 16  | 16 | U      |             | 6.           |                    |                         |      |

|     |    | rst-pe | rd_(o)      | 4-           | -                  | -                       |      |

| 17  | 17 | U      | cfer        |              |                    |                         |      |

|     |    | rst-pe | we_(o)      | -            | -                  | -                       |      |

| 18  | 18 | U      |             |              |                    |                         |      |

|     |    | rst-pe | fre_(o)     | msc0_clk(o)  | ssi0_clk(o)        | -                       |      |

| 19  | 19 | U      |             |              |                    |                         |      |

|     |    | rst-pe | fwe_(o)     | msc0_cmd(io) | ssi0_ce0_(o)       | -                       |      |

| 20  | 20 | U      | msc0_d0(io) | ssi0_dr(i)   | -                  | -                       | 1    |

| 21  | 21 | U      |             |              |                    |                         |      |

|     |    | rst-pe | cs1_(0)     | msc0_d1(io)  | ssi0_dt(o)         | -                       |      |

| 22  | 22 | U      |             |              |                    |                         |      |

|     |    | rst-pe | cs2_(0)     | msc0_d2(io)  | -                  | -                       |      |

| 23  | 23 | U      |             |              |                    |                         |      |

|     | _  | rst-pe | cs3_(0)     | msc0_d3(io)  | -                  | -                       |      |

| 24  | 24 | U      |             |              |                    |                         |      |

|     |    | rst-pe | cs4_(0)     | -            | -                  | -                       |      |

| 25  | 25 | U      |             |              |                    |                         |      |

|     |    | rst-pe | cs5_(0)     | -            | -                  | -                       |      |

| 26  | 26 | U      | cs6_(0)     | rdwr_(o)     | -                  | -                       |      |

## Table 1-1 GPIO Port A summary

2

|    |    | rst-pe |          |         |   |   |      |

|----|----|--------|----------|---------|---|---|------|

| 27 | 27 | U      | wait_(i) | -       | - | - |      |

| 28 | 28 | U      | dreq0(i) | -       | - | - |      |

| 29 | 29 | U      | dack0(o) | owi(io) | - | - |      |

| 30 | 30 | -      | -        | -       | - | - | 6    |

| 31 | 31 | -      | -        | -       | - | - | 7,11 |

# 1.1.2 GPIO Port B Summary

| Bit | PB | Pull   |               | Shared Func | tion Port Selecte | d by         |      |

|-----|----|--------|---------------|-------------|-------------------|--------------|------|

| Ν   | Ν  | (U/D)  | 0             | 1           | 2                 | 3            | Note |

| 0   | 00 | D      |               |             |                   |              | 8    |

|     |    | rst-pe | sa0_cl(o)     | -           | -                 | $-10^{112}$  | 0    |

| 1   | 01 | D      |               |             |                   | 15ed         | 9    |

|     |    | rst-pe | sa1_al(o)     | -           |                   | 75           | 5    |

| 2   | 02 | U      | sa2(o)        | -           | - nal             | -            |      |

| 3   | 03 | U      | sa3(o)        | -           | F CI II           | -            |      |

| 4   | 04 | U      | sa4(o)        | dreq1(i)    | mii_crs(i)        | -            |      |

| 5   | 05 | U      | sa5(o)        | dack1(o)    | -                 | -            |      |

| 6   | 06 | U      | cim_pclk(i)   | G. CO       | -                 | -            |      |

| 7   | 07 | U      | cim_hsyn(i)   |             | -                 | -            |      |

| 8   | 08 | U      | colum         |             |                   |              |      |

|     |    | rst-pe | • cim_vsyn(i) | -           | -                 | -            |      |

| 9   | 09 | U C    | cim_mclk(o)   | -           | -                 | epd_pwc(o)   |      |

| 10  | 10 | 10     | cim_d0(i)     | -           | -                 | epd_pwr0(o)  |      |

| 11  | 11 | D      | cim_d1(i)     | -           | -                 | epd_pwr1(o)  |      |

| 12  | 12 | U      | cim_d2(i)     | -           | -                 | epd_sce2_(o) |      |

| 13  | 13 | U      | cim_d3(i)     | -           | -                 | epd_sce3_(o) |      |

| 14  | 14 | U      | cim_d4(i)     | -           | -                 | epd_sce4_(o) |      |

| 15  | 15 | U      | cim_d5(i)     | -           | -                 | epd_sce5_(o) |      |

| 16  | 16 | D      | cim_d6(i)     | -           | -                 | epd_pwr2(o)  |      |

| 17  | 17 | D      | cim_d7(i)     | -           | -                 | epd_pwr3(o)  |      |

| 18  | 18 | D      | cim_d8(i)     | dmic_clk(o) | -                 | epd_bd0(o)   |      |

| 19  | 19 | D      | cim_d9(i)     | dmic_in(i)  | -                 | epd_bd1(o)   |      |

| 20  | 20 | U      | msc2_d0(io)   | ssi0_dr(i)  | ssi1_dr(i)        | tsd0(i)      |      |

| 21  | 21 | U      | msc2_d1(io)   | ssi0_dt(o)  | ssi1_dt(o)        | tsd1(i)      |      |

| 22  | 22 | U      | tsd2(i)       | -           | -                 | -            |      |

| 23  | 23 | U      | tsd3(i)       | -           | -                 | -            |      |

| 24  | 24 | U      | tsd4(i)       | -           | -                 | -            |      |

#### Table 1-2 GPIO Port B summary

| 25 | 25 | U      | tsd5(i)      | -            | -            | -         |  |

|----|----|--------|--------------|--------------|--------------|-----------|--|

| 26 | 26 | U      | tsd6(i)      | -            | -            | -         |  |

| 27 | 27 | U      | tsd7(i)      | -            | -            | -         |  |

| 28 | 28 | U      | msc2_clk(o)  | ssi0_clk(o)  | ssi1_clk(o)  | tsclk(i)  |  |

| 29 | 29 | U      |              |              |              |           |  |

|    |    | rst-pe | msc2_cmd(io) | ssi0_ce0_(o) | ssi1_ce0_(o) | tsstr(i)  |  |

| 30 | 30 | U      | msc2_d2(io)  | ssi0_gpc(o)  | ssi1_gpc(o)  | tsfail(i) |  |

| 31 | 31 | U      |              |              |              |           |  |

|    |    | rst-pe | msc2_d3(io)  | ssi0_ce1_(o) | ssi1_ce1_(o) | tsfrm(i)  |  |

# 1.1.3 GPIO Port C Summary

| Bit | PC                          | Pull   |              | Shared Func | tion Port Selected | d by v on | )    |

|-----|-----------------------------|--------|--------------|-------------|--------------------|-----------|------|

| Ν   | Ν                           | (U/D)  | 0            | 1           | 2                  | 3         | Note |

| 0   | 00                          | U      | lcd_b0(o)    | lcd_rev(o)  | - 1                | 7.5       |      |

| 1   | 01                          | U      | lcd_b1(o)    | lcd_ps(o)   | - nal              | -         |      |

| 2   | 02                          | U      | lcd_b2(o)    | -           | FELLE              | -         |      |

| 3   | 03                          | U      | lcd_b3(o)    | -           | 1.00               | -         |      |

| 4   | 04                          | U      | lcd_b4(o)    | - 010       | -                  | -         |      |

| 5   | 05                          | U      | lcd_b5(o)    | G. CO       | -                  | -         |      |

| 6   | 06                          | U      | Icd_b6(o)    |             | -                  | -         |      |

| 7   | 07                          | U      | lcd_b7(0)    | -           | -                  | -         |      |

| 8   | 08                          | U      | lcd_pclk(o)  | -           | -                  | -         |      |

| 9   | 09                          | ູບ   ୧ | lcd_de(o)    | -           | -                  | -         |      |

| 10  | 10                          | 1a     |              |             |                    |           |      |

|     | $\mathcal{V}_{\mathcal{O}}$ | rst-pe | lcd_g0(o)    | lcd_spl(o)  | -                  | -         |      |

| 11  | 11                          | U      | lcd_g1(o)    | -           | -                  | -         |      |

| 12  | 12                          | U      | lcd_g2(o)    | -           | -                  | -         |      |

| 13  | 13                          | U      | lcd_g3(o)    | -           | -                  | -         |      |

| 14  | 14                          | U      | lcd_g4(o)    | -           | -                  | -         |      |

| 15  | 15                          | U      | lcd_g5(o)    | -           | -                  | -         |      |

| 16  | 16                          | U      | lcd_g6(o)    | -           | -                  | -         |      |

| 17  | 17                          | U      | lcd_g7(o)    | -           | -                  | -         |      |

| 18  | 18                          | U      | lcd_hsyn(io) | -           | -                  | -         |      |

| 19  | 19                          | U      | lcd_vsyn(io) | -           | -                  | -         |      |

| 20  | 20                          | U      | lcd_r0(o)    | lcd_cls(o)  | -                  | -         |      |

| 21  | 21                          | U      | lcd_r1(o)    | -           | -                  | -         |      |

| 22  | 22                          | U      | lcd_r2(o)    | -           | -                  | -         |      |

| 23  | 23                          | U      | lcd_r3(o)    | -           | -                  | -         |      |

#### Table 1-3 GPIO Port C summary

4

| 24 | 24 | U      | lcd_r4(o)     | - | - | - |  |

|----|----|--------|---------------|---|---|---|--|

| 25 | 25 | U      | lcd_r5(o)     | - | - | - |  |

| 26 | 26 | U      | lcd_r6(o)     | - | - | - |  |

| 27 | 27 | U      | lcd_r7(o)     | - | - | - |  |

| 28 | 28 | U      | uart2_rxd(i)  | - | - | - |  |

| 29 | 29 | U      | uart2_cts_(i) | - | - | - |  |

| 30 | 30 | U      |               |   |   |   |  |

|    |    | rst-pe | uart2_txd(o)  | - | - | - |  |

| 31 | 31 | U      |               |   |   |   |  |

|    |    | rst-pe | uart2_rts_(o) | - | - | - |  |

# 1.1.4 GPIO Port D Summary

| N                               | N         (L           00         -           01         -           02         -           03         -           04         -           05         -           06         -           07         - | Pull       J/D)       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U       U | 0<br>pcm0_do(o)<br>pcm0_clk(io)<br>pcm0_syn(io)<br>pcm0_di(i)<br>ps2_mclk(io)<br>ps2_mdata(io)<br>ps2_kclk(io) | Shared Funct<br>1<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | tion Port Selected | 1 by <u>0</u><br>3<br>-<br>-<br>-<br>-<br>- | Note |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------|---------------------------------------------|------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6 | 00           01           02           03           04           05           06           07                                                                                                        | U<br>U<br>U<br>U<br>U<br>U<br>U<br>U<br>U                                                                                                                                                                                                                       | pcm0_do(o)<br>pcm0_clk(io)<br>pcm0_syn(io)<br>pcm0_di(i)<br>ps2_mclk(io)<br>ps2_mdata(io)                      | -<br>-<br>- 11<br>- 011                                                            | -<br>ternal<br>-   | -                                           | Note |

| 1<br>2<br>3<br>4<br>5<br>6      | 01<br>02<br>03<br>04<br>05<br>06<br>07                                                                                                                                                               | U<br>U<br>U<br>U<br>U<br>U<br>U                                                                                                                                                                                                                                 | pcm0_clk(io)<br>pcm0_syn(io)<br>pcm0_di(i)<br>ps2_mclk(io)<br>ps2_mdata(io)                                    | -<br>- jr<br>011                                                                   | terna<br>-         | -                                           |      |

| 2<br>3<br>4<br>5<br>6           | 02<br>03<br>04<br>05<br>06<br>07                                                                                                                                                                     | U<br>U<br>U<br>U<br>U                                                                                                                                                                                                                                           | pcm0_syn(io)<br>pcm0_di(i)<br>ps2_mclk(io)<br>ps2_mdata(io)                                                    | - ir                                                                               | terr<br>-<br>-     | -                                           |      |

| 3<br>4<br>5<br>6                | 03<br>04<br>05<br>06<br>07                                                                                                                                                                           | U<br>U<br>U<br>U                                                                                                                                                                                                                                                | pcm0_di(i)<br>ps2_mclk(io)<br>ps2_mdata(io)                                                                    |                                                                                    | -                  | -                                           |      |

| 4<br>5<br>6                     | 04<br>05<br>06<br>07                                                                                                                                                                                 | U<br>U<br>U                                                                                                                                                                                                                                                     | ps2_mclk(io)<br>ps2_mdata(io)                                                                                  | $-cO^{\mu}$                                                                        | -                  |                                             |      |

| 5<br>6                          | 05<br>06<br>07                                                                                                                                                                                       | U<br>U                                                                                                                                                                                                                                                          | ps2_mdata(io)                                                                                                  | <u>6</u> .                                                                         | -                  | -                                           |      |

| 6                               | 06<br>07                                                                                                                                                                                             | U                                                                                                                                                                                                                                                               |                                                                                                                |                                                                                    |                    |                                             | 1    |

|                                 | 07                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                 | ps2_kclk(io)                                                                                                   |                                                                                    | -                  | -                                           |      |

| 7                               | -                                                                                                                                                                                                    | U -                                                                                                                                                                                                                                                             |                                                                                                                | -                                                                                  | -                  | -                                           |      |

|                                 | 08                                                                                                                                                                                                   | /                                                                                                                                                                                                                                                               | ps2_kdata(io)                                                                                                  | -                                                                                  | -                  | -                                           |      |

| 8                               |                                                                                                                                                                                                      | υC                                                                                                                                                                                                                                                              | scc_data(io)                                                                                                   | -                                                                                  | -                  | -                                           |      |

| 9                               | 09                                                                                                                                                                                                   | D                                                                                                                                                                                                                                                               | scc_clk(o)                                                                                                     | clk48m(i)                                                                          | -                  | -                                           |      |

| 10                              | 10                                                                                                                                                                                                   | U                                                                                                                                                                                                                                                               | pwm6(io)                                                                                                       | -                                                                                  | -                  | -                                           |      |

| 11                              | 11                                                                                                                                                                                                   | U                                                                                                                                                                                                                                                               | pwm7(io)                                                                                                       | -                                                                                  | -                  | -                                           |      |

| 12                              | 12                                                                                                                                                                                                   | D                                                                                                                                                                                                                                                               | uart3_rxd(i)                                                                                                   | bclk0(io)                                                                          | -                  | epd_pwr4(o)                                 |      |

| 13                              | 13                                                                                                                                                                                                   | D                                                                                                                                                                                                                                                               | Irclk0(io)                                                                                                     | -                                                                                  | -                  | epd_pwr5(o)                                 |      |

| 14                              | 14                                                                                                                                                                                                   | U                                                                                                                                                                                                                                                               | -                                                                                                              | -                                                                                  | -                  | -                                           | 10   |

| 15                              | 15                                                                                                                                                                                                   | D                                                                                                                                                                                                                                                               |                                                                                                                |                                                                                    |                    |                                             |      |

|                                 | rs                                                                                                                                                                                                   | st-pe                                                                                                                                                                                                                                                           | exclk(o)                                                                                                       | -                                                                                  | -                  | -                                           |      |